## Example: Another CMOS Logic Gate Synthesis

Now let's design a gate that realizes this Boolean algebraic expression:

$$\mathbf{Y} = \left(\overline{\mathbf{A}} + \overline{\mathbf{B}}\right)\mathbf{C}$$

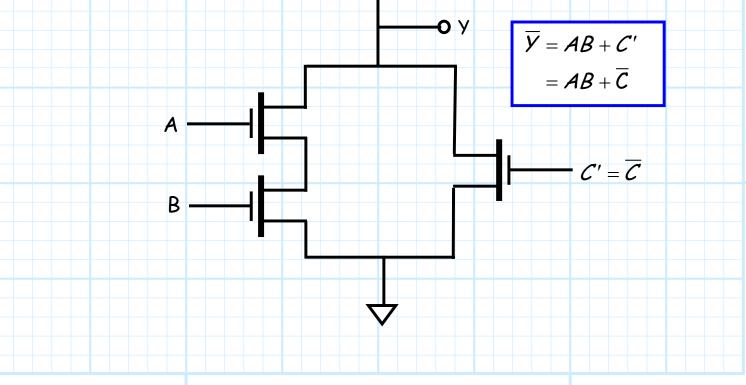

Step 1: Design PDN

First, let's rewrite Boolean expression as  $\overline{Y} = f(A,B,C)$ :

$Y = (\overline{A} + \overline{B})C$  $\overline{Y} = \overline{(\overline{A} + \overline{B})C}$  $\overline{Y} = (\overline{\overline{A} + \overline{B}}) + \overline{C}$  $\overline{Y} = AB + \overline{C}$

**Q**: Yikes! We cannot write this expression explicitly in terms of **uncomplemented** inputs A, B, and C! The input C appears as  $\overline{C}$  in the expression. What do we do **now**?

$C' = \overline{C}$

A: An easy problem to solve! We can essentially make a substitution of variables:

## And thus:

Therefore, the inputs to this logic gate should be A, B, and C' (i.e, A, B, and the complement of C ).

$\overline{\mathbf{Y}} = \mathbf{A}\mathbf{B} + \mathbf{C}'$

Note that this Boolean expression "says" that:

"The ouput is low if either, A AND B are both high, OR C' is high"

Of course another way of "saying" this is:

"The output is low if either A AND B are both high, OR C is low"

The PDN is therefore:

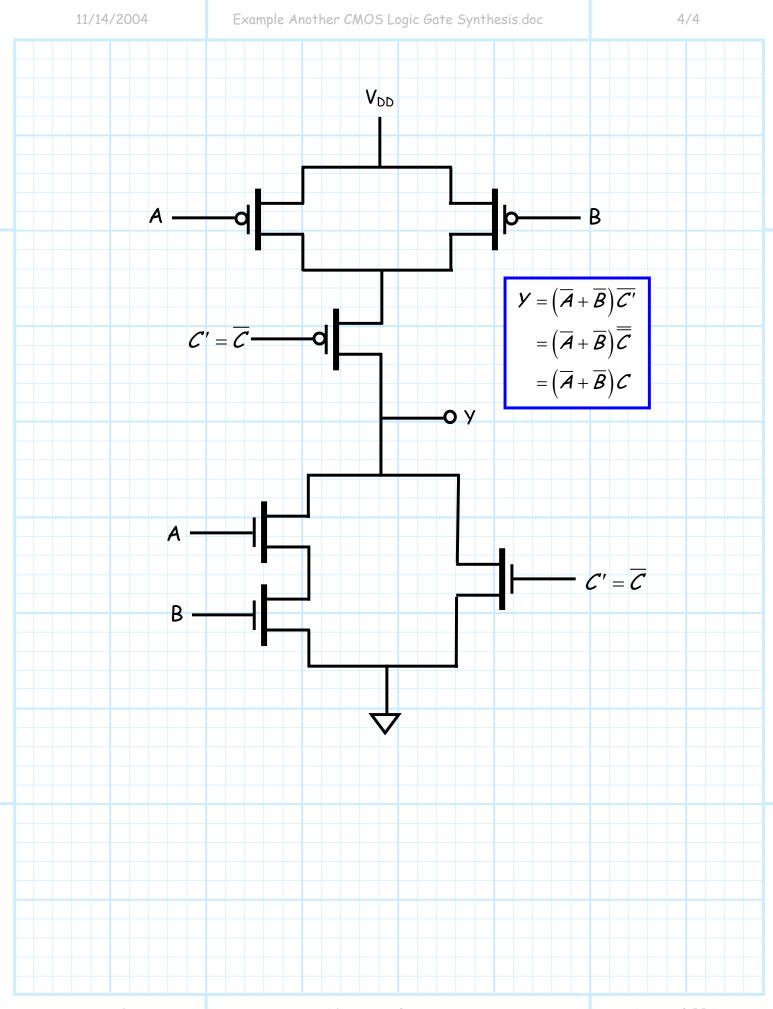

## **Step 2:** Design the PUN

Note we have as similar problem as before—the expression for Y **cannot** explicitly be written in terms of complemented inputs  $\overline{A}$ ,  $\overline{B}$ , and  $\overline{C}$ :

$$\mathbf{Y} = \left(\overline{\mathbf{A}} + \overline{\mathbf{B}}\right)\mathbf{C}$$

Note we can again solve this problem by using the same substitution of variable C:

$$C' = \overline{C}$$

$\overline{C'} = C$

Therefore:

$$\mathbf{Y} = \left(\overline{\mathbf{A}} + \overline{\mathbf{B}}\right)\overline{\mathbf{C}'}$$

$$= \left(\overline{\mathbf{A}} + \overline{\mathbf{B}}\right)\mathbf{C}$$

This expression "says" that:

"The output will be high if, either A OR B are low, AND C' is low"

Which is equivalent to saying:

"The output will be high if, either A OR B are low, AND C is high"

The CMOS digital logic device is therefore: